# A Low Power Class-AB Audio Power Amplifier With Dynamic Transconductance Compensation in 55 nm CMOS Process

Fang Tang, Member, IEEE, Shiping Li, Bo Wang, Student Member, IEEE, Amine Bermak, Fellow, IEEE, Xichuan Zhou, Member, IEEE, and Shengdong Hu

Abstract—This paper presents a Class-AB audio power amplifier with state-of-the-art power efficiency and performance. In this work, the second stage transconductance of the three-stage power amplifier can be dynamically compensated, in order to automatically adjust the amplifier pole according to the operating condition of the output stage. Working with a current sensing module, the proposed dynamic transconductance compensation scheme is more power-efficient to allocate the frequency of nondominant-pole under a specified stability requirement. A prototype chip is designed and fabricated using 55 nm CMOS process. The measured static current consumption of the core circuit is 0.35 mA with a 1.8 V supply voltage. -85 dB THD+N, 106 dB signal dynamic range and 55 mW output power are verified in silicon under a wide range of load capacitance from 5 pF to 20 nF. Measurement result shows the proposed transconductance compensation technique is effective in both constant voltage supply mode and dynamic supply (Class-G) mode.

Index Terms—Audio power amplifier, class-AB, CMOS integrated circuit, low power.

#### I. INTRODUCTION

**N** OWADAYS, high performance headphone power amplifier (PA) gains rapidly increased applications in high-end products like high-fidelity audio players and mobile phones. The main specifications of an audio power amplifier include: maximum output power, total harmonic distortion + noise (THD+N), dynamic range, static power consumption, clickpop noise, power supply rejection ratio (PSRR), offset, chip area, etc. [1]. Since most of these specifications are correlated, higher specifications, like THD+N or DR, would then penalize the power consumption. An optimal way to design the PA is to make good trade-off based on its target application [2].

Manuscript received November 26, 2015; revised March 4, 2016 and April 30, 2016; accepted June 3, 2016. Date of publication August 17, 2016; date of current version September 2, 2016. This work was supported by National Natural Science Foundation of China, No. 61404016 and No. 61471071 and also supported by the Fundamental Research Funds for the Central Universities Project No. 106112016CDIZR168803. This paper was recommended by Associate Editor N. Maghari. (*Corresponding author: Xinchuan Zhou.*)

F. Tang, S. Li, X. Zhou, and S. Hu are with the the College of Communication Engineering, Chongqing University (CQU), Chongqing 63004, China (e-mail: zxc@cqu.edu.cn).

B. Wang is with the Massachusetts Institute of Technology (MIT) Cambridge, MA 02139 USA, and also with Hong Kong University of Science and Technology, Kowloon, Hong Kong.

A. Bermak is with the College of Science and Engineering, Hamad Bin Khalifa University, Ar-Rayyan, Qatar, and also with Hong Kong University of Science and Technology, Kowloon, Hong Kong.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2016.2586199

In some low-end products, two-stage amplifier with a moderate DC open-loop gain is adopted, which is easy to be kept stable even under large load variations, while with inferior harmonic distortion [3]. For better closed-loop linearity, threestage Class-AB mode amplifier topology has gained more attention in the past decade for its higher gain and better power efficiency with the capability to handle a wide range of capacitive load [4]. Although frequency compensation technique of damping-factor-control was proposed [5], conventional Class-AB driver is not an optimal solution for a signal with large real-time amplitude variation. Because the transconductance  $(g_m)$  of the output stage significantly changes as a function of the output current amplitude, the relative frequency space between the gain-bandwidth (GBW) and the non-dominant-pole could vary. As a result, to guarantee the closed-loop stability of the amplifier, it is over-designed for the worst phase margin scenario, which burns more than necessary power during normal operation. To address this overcompensation issue, reference [6] introduced a low power Class-AB/B hybrid PA scheme at the cost of design complexity and chip area for the Class-B integration. Voltage level shifters were used to enable the Class-B driver if the signal became larger than a threshold voltage. To further improve the power efficiency, current sensing technique was introduced into headphone drivers [7]. For a small output signal, a conventional Class-AB driver was adopted. As the output signal increased, the proposed PA could gradually turn on the auxiliary Class-B driver, by monitoring the output current using a  $g_m$ replica circuit. Inductor current sensing technique was also widely adopted in Class-D headphone drivers but mainly for the speaker protection purpose [8]–[10].

In this paper, an audio power amplifier designed in 55 nm CMOS process is presented, which is embedded as a key building block in a system-on-chip (SOC). A power-efficient frequency compensation scheme for the Class-AB driver is proposed with a dynamic transconductance adjustment circuit. With an dedicated output current sensing module, the current-to-voltage control signals can dynamically adjust the MOS resistors inside the second stage of the main amplifier and thus optimize the pole location. Compared with a conventional Class-AB, the proposed scheme can reduce the power waste for frequency over-compensation when given a specified stability requirement. The proposed transconductance compensation scheme is verified in both constant voltage supply mode and dynamic supply (Class-G) mode.

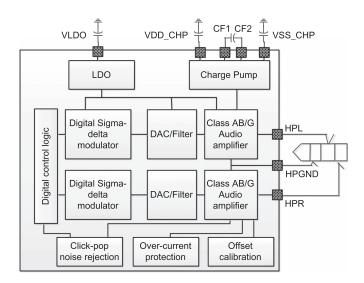

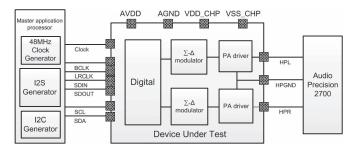

Fig. 1. Top architecture of the proposed audio power amplifier chip.

This paper is organized as follows. In Section II, the power amplifier circuit is analyzed. Section III presents the circuit implementation. Section IV demonstrates the experimental result, followed by the conclusion in Section V.

# II. PROPOSED INTEGRATED STEREO POWER AMPLIFIER TOPOLOGY

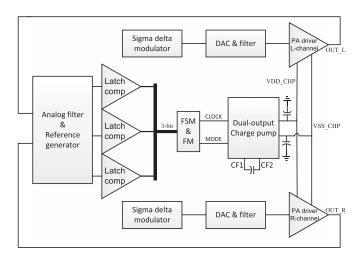

Fig. 1 shows the top architecture of the proposed audio power amplifier. The input digital signal is modulated by the digital sigma-delta modulator and thus, most of the quantization noise is shaped into the high frequency band. The input digital signal is converted into the analog signal in the audio frequency band of 20 KHz and is processed by a following analog filter. The audio signal in its analog form is then amplified by the Class-AB power amplifier. A single-flying capacitor charge pump generates both positive and negative supply voltages for the output driver stage [11]. This dedicated power supply can isolate the internal noise-sensitive circuits from the output power supply noise. The first two stages of the power amplifier use 1.8 V analog supply and ground while the third Class-AB stage operates with +/-1.8 V power supply generated from the charge pump. In Class-G mode, if the input signal amplitude is large, the charge pump provides +/-1.8 V for the power amplifier, otherwise +/-0.9 V are generated. The supply voltage can be switched smoothly to prevent any obvious crossover distortion [7]. The click pop noise suppression circuit can attenuate the click pop noise during power on and off. The offset calibration circuit dynamically measures the output offset voltage and then adjust the DC bias.

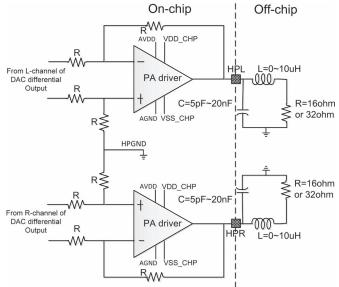

Fig. 2 shows the zoom-in structure of the power amplifier block, including both right and left sound channels with two differential-to-single-ended amplifiers. From the perspective of different application scenarios, the proposed driver can tolerate various load conditions ranging from 5 pF to 20 nF, 0 H to 10  $\mu$ H, 16 ohm or 32 ohm, as required in consumer electronics [12].

Fig. 2. Zoom-in structure of the power amplifier block.

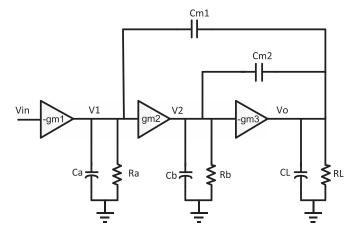

Fig. 3. A standard three-stage amplifier with Nested Miller compensation.

# **III. POWER AMPLIFIER CIRCUIT SCHEME**

#### A. Three-Stage Amplifier

Fig. 3 shows the simplified model of a standard three-stage amplifier with Nested-Miller-Compensation (NMC) [13]. Assuming the transconductance of each stage is  $g_{mi}$ , the local RC parameter of each stage is  $R_aC_a$ ,  $R_bC_b$ ,  $R_LC_L$  and the Miller compensation capacitors are  $C_{m1}$  and  $C_{m2}$ , respectively. The open-loop gain  $A_0$  as well as dominant/non-dominant poles  $p_1 \sim p_3$  of the whole amplifier can be approximated as (1)–(3) [14], [15]

$$A_0 = g_{m1} g_{m2} g_{m3} R_a R_b R_L \tag{1}$$

$$p_1 \approx \frac{1}{g_{m2}g_{m3}R_a R_b R_L C_{m1}} \tag{2}$$

$$p_{2,3} \approx \frac{g_{m3} - g_{m2}}{2C_L} \pm j \frac{g_{m3} - g_{m2}}{2C_L}.$$

(3)

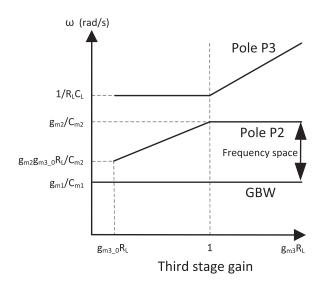

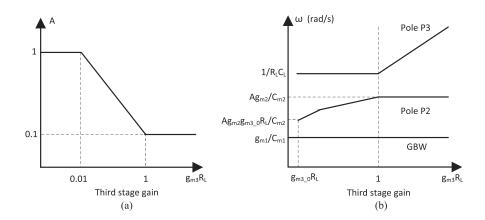

Fig. 4. Typical relationship between GBW, poles and the third stage gain.

The poles from Miller effect need keep stable [16]. Since the output load resistance could be lower to 16 ohm, Class-AB is required for low static power design. Along with the large variation of the third stage transconductance  $g_{m3}$ , the output stage gain is also changed as a function of the output current amplitude. Variable  $g_{m3}$  implies that the Miller effect pole location is unfixed. With a large output drive current,  $g_{m3}R_L \gg 1$ thus,  $p_2 = g_{m2}/C_{m2}$  and  $p_3 = g_{m3}/C_L$  [15]. On the contrary, for a small static current,  $g_{m3}R_L \ll 1$ ,  $p_2$  and  $p_3$  can be approximately expressed as

$$p_2 = \frac{g_{m2}g_{m3}R_L}{C_{m2}} \tag{4}$$

$$p_3 = \frac{1}{(R_L C_L)}.$$

(5)

Defined by the product of the DC-gain and the dominant pole frequency, the gain-bandwidth (GBW) product (the same as unit-gain-frequency for a single pole system) of the three-stage amplifier exhibits a constant value, as expressed in (6). The frequency locations of  $p_2$  and  $p_3$  as a function of the third stage gain  $g_{m3}R_L$  can be illustrated in Fig. 4. When  $g_{m3}R_L < 1$ ,  $p_2$  follows  $g_{m3}$  from a tiny value of  $g_{m2}g_{m3_0}R_L/C_{m2}$  to  $g_{m2}/C_{m2}$ , where  $g_{m3_0}$  is the transconductance of the output stage with a nil load current amplitude. Different from  $p_2$ ,  $p_3$ is almost fixed until  $g_{m3}R_L > 1$  and then it begins to move to the high frequency. The minimum frequency of  $p_2$  happens at  $g_{m3_0}$ , as derived in (7) where  $W_{17}$ ,  $W_{19}$ ,  $L_{17}$ ,  $L_{19}$  are the width and length for transistor  $M_{17}$  and  $M_{19}$  in Fig. 9

$$\mathbf{GBW} = A_0 \times p_1 = \frac{g_{m1}}{C_{m1}} \tag{6}$$

$$p_{2} = \frac{g_{m2}g_{m3_{0}}R_{L}}{C_{m2}}$$

$$= g_{m2}\sqrt{\frac{2I_{s}}{C_{ox}}}\left(\sqrt{\frac{W_{17}}{\mu_{p}L_{17}}} + \sqrt{\frac{W_{19}}{\mu_{n}L_{19}}}\right)\frac{R_{L}}{C_{m2}}.$$

(7)

# B. Proposed Dynamic Transconductance Compensation

The principle of frequency compensation in a multi-stage amplifier is to split the GBW and non-dominant poles by Miller effect until their relative frequency space is large enough to provide a specified phase margin. Shown in Fig. 4, the frequency space must fulfill the phase margin specification at the worst condition of  $g_{m3_0}$ . As a result, the frequency space is over-designed for a larger  $g_{m3}$ , implying that power saving can be achieved by optimizing  $g_{m2}$  correspondingly after monitoring  $g_{m3}$ .

A dynamic transconductance compensation (or modulation) technique is proposed to balance the frequency space between the gain-bandwidth and non-dominant-pole as a function of  $g_{m3}$ . To better describe the proposed scheme, a normalized transconductance adjustment factor A is introduced, where it can be seen as a function of the third stage transconductance  $g_{m3}$ . When  $g_{m3}R_L \ll 1$ , A is designed to be much larger than that when  $g_{m3}R_L > 1$ , as shown in Fig. 5(a). Assisted by the adjustment factor A, the frequency space can be increased for a small  $g_{m3}$  and decreased for a large  $g_{m3}$ , as illustrated in Fig. 5(b). Compared to Class-AB power amplifiers with the conventional Miller compensation method,  $p_2$  in this design exhibits less frequency variation and therefore less power consumption is wasted for over-compensation in the large output current situation.

# C. Amplifier Circuit Implementation

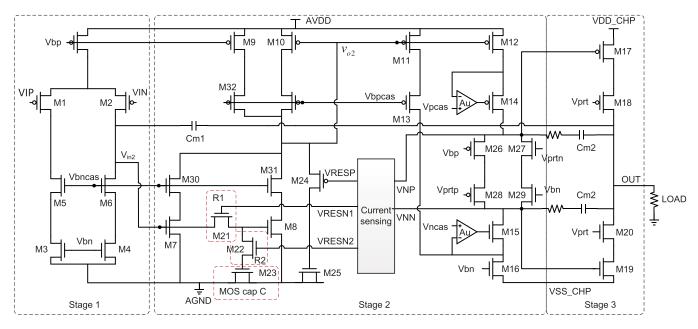

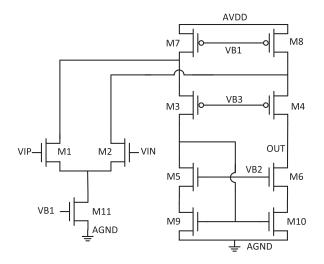

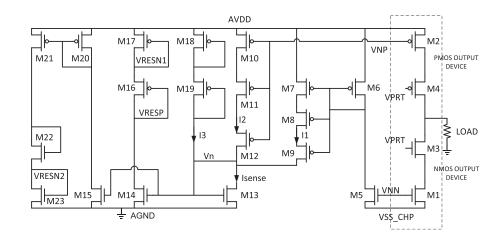

Fig. 6 shows the simplified transistor-level schematic of the proposed Class-AB driver. It consists of a telescopic input stage, a current-mode folded second stage, a push-pull Class-AB output stage and a dynamic transconductance compensation function with a current sensing block. The sensed output current amplitude (or  $g_{m3}$  of the third stage) is used to generate the control signals VRESN1 and VRESN2 to adjust the variable resistors  $R_1$  and  $R_2$ , which are implemented with  $M_{21}$  and  $M_{22}$ , respectively. VRESP is a fine control signal to tune the transconductance  $g_{mM_{24}}$  of  $M_{24}$ . Two moscaps  $M_{23}$ and  $M_{25}$  are used for low frequency signal blockage. Inside the second stage, transistors  $M_{26} \sim M_{29}$  are used as a translinear loop floating control to guarantee the stability of the output stage at different process corners.  $M_{14}$  and  $M_{15}$  are used for gain boosting assisted with the auxiliary amplifier  $A_u$  [17]. Fig. 7 shows the schematic of the N-type folded-cascode auxiliary amplifier to regulate  $M_{14}$  while a PMOS-input-pair version is adopted for  $M_{15}$ . Both Ahuja [18] and Miller compensation techniques are adopted in the proposed driver in order to save power as well as chip area for large capacitive loads. The Ahuja/Miller hybrid scheme is also helpful to extend the amplifier bandwidth at the cost of more complicated compensation circuit [19]. Cascode transistors  $M_{18}$  and  $M_{20}$  are used in the third stage to improve the output impedance.

The first and second stages of the amplifier utilize 1.8 V power supply from the same LDO. The first stage ground is a clean analog 0 V. The negative power supply of the second and third stages and the positive power of the third stage are supplied from a dedicated charge pump module. By such a power planning, the whole system enjoys a better noise isolation and

Fig. 5. (a) Proposed relationship between adjustment factor A and the third stage gain; (b) proposed relationship between GBW, poles and the third stage gain.

Fig. 6. Proposed Class-AB driver schematic.

Fig. 7. The schematic of the N-type auxiliary amplifier for cascode PMOS transistor regulation.

the input referred noise is attenuated by the high open-loop gain. By adding the cascode structure with proper bias voltages (Vncas, Vbcas, Vprt, Vbpcas, Vbncas, etc), unsafe transistor operation points are avoided [17]. At the worst case, this threestage amplifier has a simulated open-loop gain of 102 dB with 6 MHz unit gain frequency and 70° phase margin. The feedback factor is designed to offer a closed-loop gain tuning range from -6 dB to 6 dB.

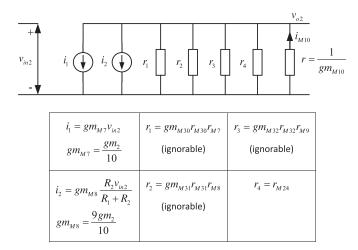

Fig. 8 shows the simplified small signal model of the proposed dynamic transconductance compensation function of the second stage, where *i* and *r* are small signal symbols of the current and equivalent resistor, respectively. As a result,  $i_{M10}$  flowing through  $M_{10}$  can be expressed as (8), (9)

$$i_{M10} = i_1 + i_2 + \frac{v_{o2}}{r_1} + \frac{v_{o2}}{r_2} + \frac{v_{o2}}{r_3} + \frac{v_{o2}}{r_{M24}}$$

(8)

$$v_{o2} = \frac{-i_{M10}}{g_{m\,M10}} \tag{9}$$

$$i_{M10} \approx i_1 + i_2 - \frac{i_{M10}}{r_{M24}g_{mM10}} \tag{10}$$

$$i_1 = \frac{g_{m_2}}{10} v_{\text{in2}} \tag{11}$$

$$i_2 = \frac{9g_{m_2}R_2v_{\text{in}2}}{10(R_1 + R_2)}.$$

(12)

Fig. 8. Small signal model of the proposed dynamic transconductance compensation function in the second stage of the amplifier.

Assuming  $r_1 \sim r_3$  are much larger than  $r_4$ , by combining (10)–(12),  $i_{M10}$  can be expressed as (13), where  $g_{m2}$  is defined as the conventional second stage transconductance without using the proposed dynamic transconductance compensation function. After the equation rearrangement in (14), the second stage transconductance adjustment factor A becomes a function of  $R_1$  and  $R_2$ , which can automatically follow the output stage operation condition:

$$i_{M10} = \frac{g_{m2}v_{\text{in}2}R_1 + 10g_{m2}v_{\text{in}2}R_2}{10\left(1 + \frac{1}{r_{M24}g_{m_{M10}}}\right)\left(R_1 + R_2\right)}$$

(13)

$$i_{M10} = Ag_{m_2}v_{\text{in}2}$$

$$\Rightarrow A = \frac{R_1 + 10R_2}{10\left(1 + \frac{1}{r_{M24}g_{m_{M10}}}\right)(R_1 + R_2)}.$$

(14)

When the output current has a small amplitude,  $r_{M24}g_{mM10} \gg 1$  and  $R_1 \ll R_2$  thus,  $A \approx 1$ . On the contrary, for a large output current,  $R_1 \gg R_2$  and A can be approximated as

$$A_{Io} \approx \frac{1}{10\left(1 + \frac{gm_{M24}}{gm_{M10}}\right)}$$

(15)

The schematic of the proposed current sensing circuit used in Fig. 6 is shown in Fig. 9. The output currents of Class-AB driver transistors  $M_1$  and  $M_2$  are mirrored and added as a control signal  $I_{\text{sense}}$  as expressed in (16), where transistors have the same channel length and  $I_3$  is used to adjust the offset of  $I_{\text{sense}}$ . For a large output current instantaneous amplitude (> 10 uA),  $I_3$  can be ignored. For nil output (< 100 nA),  $I_3$  makes sure transistors of the current sensing circuit operating in the saturation region. Process, voltage and temperature (PVT) variations can be tolerated by specified phase margin of the amplifier

$$I_{\text{sense}} = |I_{M1}| \frac{W_5 W_7}{W_1 W_6} + |I_{M2}| \frac{W_{10}}{W_2} + I_3.$$

(16)

Voltage VRESN1 and VRESN2 automatically follow the sensed output current. According to the simulation, for  $I_1 = 0.5 \ \mu$ A,  $M_{17}$  and  $M_{23}$  in Fig. 9 set VRESN1 = 1.2 V and

VRESN2 = 0.6 V. As a result, in Fig. 6 MOS resistor  $M_{21} \gg M_{22}$ . When the sensed current becomes larger than the specified critical high value  $I_1 = 10 \ \mu$ A, the control voltages are VRESN1 = 0.75 V and VRESN2 = 1 V. At this condition,  $M_{21}$  in Fig. 6 enters into the cutoff region. As current  $I_1$  continuously increased, since  $M_{21}$  is already cutoff, it cannot further contribute transconductance adjustment. Because all of the internal nodes in the current sensor circuit exhibit low impedances, the response time of this control loop is less than 50 ns, which can be ignored.

It should be noted that, the DC current consumption in the proposed design remains the same in different output conditions. But in order to achieve the same DC-gain, bandwidth and stability requirement, a conventional design with fixed equivalent second stage transconductance must consume more power. The power saving in the proposed circuit can be achieved at the large value of  $g_{m3}R_L$  (right region of Fig. 5(b)) by reducing the adjustment factor A. As shown in (3), the dominant pole  $p_1$  is reversely proportional to  $g_{m2}g_{m3}$ . Therefore, the openloop -3 dB bandwidth drops for a large  $g_{m3}$ , while the phase margin (or stability) degrades for a small  $g_{m3}$ . To move the non-dominant pole  $p_2$  to higher frequency for a small  $g_{m3}$ ,  $g_{m2}$  should be a large value which is comparable for both the conventional and proposed designs. The difference is that, in the conventional design,  $g_{m2}$  is a constant value, however, in the proposed design, when the instantaneous load current amplitude becomes large, the equivalent  $g_{m2}$  is only 10% of that in the conventional design. As a result,  $p_1$  in the conventional design could be much smaller due to a larger  $g_{m2}g_{m3}$ . In order to increase  $p_1$  (or bandwidth),  $R_a$  or  $R_b$  or  $C_{m1}$  must be reduced, as shown by (3). If  $R_a$  or  $R_b$  is set to a small value by utilizing short channel length transistors (smaller  $\lambda$ ), the DC-gain lose must be compensated with extra current consumption by increasing  $g_{m1}$  or other parameters. If  $C_{m1}$  is sized with a small value, although the DC-gain is not affected,  $g_{m1}$  must be reduced in order to keep the same GBW, which also implies sacrificing the DC-gain. In our proposed design, the DC-gain is not affected by the dynamic transconductance adjustment due to the existence of DC blockage MOS capacitors  $M_{23}$  and  $M_{25}$ . At the high frequency, the equivalent  $g_{m2}$ is reduced when  $g_{m3}$  increased. Therefore, the degradation of  $p_1$  as a function of  $g_{m3}$  is power-efficiently attenuated by the proposed technique without changing the DC-gain.

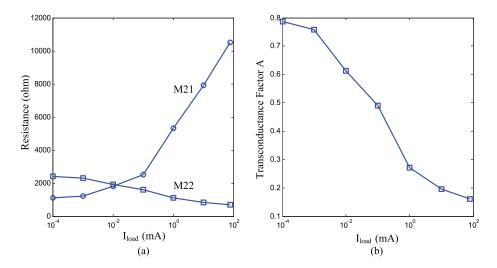

According to the simulation, the proposed method can save 10% the total power of the amplifier compared to the conventional design at large values of  $g_{m3}$ . Fig. 10 shows the simulation results for equivalent MOSFET resistances of  $M_{21} \sim M_{22}$  and the transconductance adjustment factor A, as a function of the output load current amplitude. It indicates that the control sensitivity of the factor A at  $I_{\text{load}} = 0.1$  mA is about 0.35/decade.

#### D. Class-G Mode

The proposed chip also supports the feature of dynamic power supply conditioning (Class-G mode), where the supply voltage can automatically switch between +/-0.9 V and +/-1.8 V. Fig. 11 shows the block diagram of the Class-G

Fig. 9. Proposed current sensing circuit schematic, where transistors  $M_1 \sim M_4$  are the same as transistors  $M_{17} \sim M_{20}$  in Fig. 6.

Fig. 10. The simulation results for (a) equivalent MOSFET resistances of  $M_{21} \sim M_{22}$  and (b) the transconductance compensation factor A, as a function of the output load current amplitude.

Fig. 11. Block diagram of the dynamic supply conditioning.

scheme. The power amplifier output is firstly low-pass filtered to attenuate the out-audio-band high frequency noise and then quantized by three hysteresis comparators which form a 2-bit flash A/D converter. The reference voltage for each hysteresis comparator can also be adjusted by programming the on-chip registers through the peripheral  $I^2C$  or  $I^2S$  communication interface. The quantized digital code is further processed in the digital logic block to create the control signals for the adaptive power supply conditioning. Moreover, efforts are made to guarantee the low switching distortion during the operation mode change. Supply voltage is changed with a limited slew rate, which can reduce the directly coupled switching noise in the output voltage. Limited slew rate of the supply voltage in the output stage will not significantly increase the harmonic distortion, since the high open-loop gain of the first two stages can attenuate the impact due to supply voltage variation of the third stage. In order to save the switching power, phase modulator and clock frequency modulator are also adopted to avoid frequently switching the charge pump operating mode.

#### **IV. MEASUREMENT RESULTS**

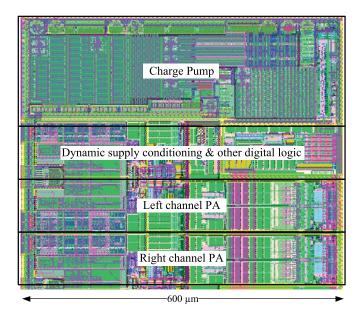

The proposed chip is designed and fabricated using CMOS 55 nm process and Fig. 12 shows the designed chip layout with partitioning of main blocks. The designed input signal amplitude range is from -110 dBV to 0 dBV. The threshold

Fig. 12. Layout of the fabricated chip.

Fig. 13. Chip test environment setup.

voltage used for Class-G mode to switch the supply voltage is 550 mV. The switching frequency of the charge pump can be set from 1 MHz to 10 MHz. The charge pump is located at the top of the chip. The bottom half of the chip is the left/right audio channels and other analog circuits, while the digital circuit is mainly placed in the middle with noise isolation guardring. Fig. 13 illustrates the chip testing platform including the master application processor, device under test (DUT) and audio signal performance test equipment AP2700 [20]. The master application processor generates all the control logics and clocks as well as I2S and I2 C bus signals. The DUT as a slave device processes the input data to drive the test equipment AP2700. The static current consumption of the core chip is 350  $\mu$ A with a 16 ohm resistive load, in which the PA, the charge pump and the rest control modules consumes 250  $\mu$ A, 80  $\mu$ A and 20  $\mu$ A, respectively. The achieved output power is 55 mW for 1% THD+N [22].

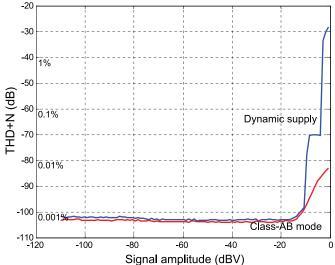

Fig. 14 indicates the waveform of the measured A-weighted THD+N versus input signal amplitude. Input signal frequency is 1 KHz and the noise bandwidth is from 20 Hz to 20 KHz. The number of harmonics is 20 and the capacitive load is 1 nF. For Class-AB mode, the entire audio driver achieves 106 dB A-weighted dynamic range under 16 ohm load with a close-loop gain range from -6 dB to 6 dB. When operating under dynamic supply conditioning mode, the dynamic range can

Fig. 14. Measured A-weighted THD+N versus input signal amplitude with 1 KHz signal frequency, 0 dB gain, 20 Hz to 20 KHz noise band, 20 harmonics and 1 nF capacitive load.

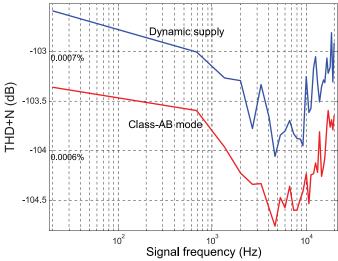

Fig. 15. Measured A-weighted THD+N versus input signal frequency with -60 dBV signal amplitude, 0 dB gain, 20 Hz to 20 KHz noise band, 20 harmonics and 1 nF capacitive load.

still achieve better than 104 dB. It is clear that, when larger than -15 dBV, the signal amplitude can significantly affect the linearity and Class-AB performs much better than dynamic supply conditioning for a very large signal amplitude.

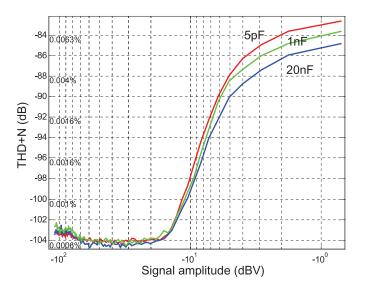

Fig. 15 shows the waveform of THD+N versus input signal frequency under -60 dBV input signal amplitude with similar test conditions as Fig. 14, which proves that the dynamic range is almost constant in the whole audio band from 20 Hz to 20 KHz. Fig. 16 shows the measurement result of THD+N under different load capacitance of 5 pF, 1 nF and 20 nF for Class-AB mode. For less than -15 dBV signal amplitude, the THD+N is hardly affected by the load capacitance and both normal Class-AB and dynamic supply conditioning feature have very stable performance.

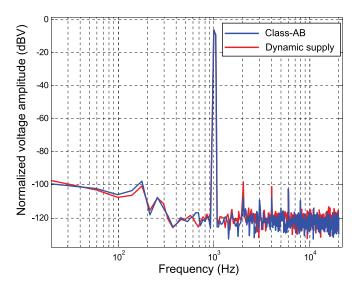

The FFT measurement result for Class-AB and dynamic supply conditioning modes are depicted in Fig. 17 with

Fig. 16. Measured A-weighted THD+N versus input signal amplitude in Class-AB mode, under different load capacitances, 5 pF, 1 nF, 20 nF with 1 KHz signal frequency, 0 dB gain, 20 Hz to 20 KHz noise band, 20 harmonics and 16 ohm resistive load.

Fig. 17. Measured FFT for Class-AB and dynamic supply conditioning modes with 8192 sampling points with 0 dB gain, 1 nF and 16 ohm load.

8192 sampling points, which shows similar noise floors in both two modes. Supply conditioning introduces a little bit higher noise floor because the switching noise of the charge pump is incompletely attenuated by the loop gain. Moreover, the second order harmonic distortion is only about 9 dB less than that of the third order due to the adopted pseudo-differential architecture [21].

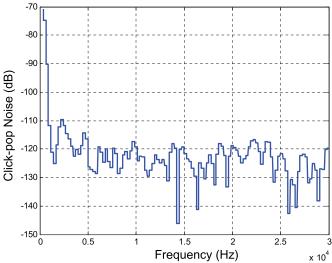

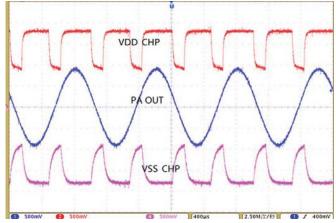

The measurement result of click-pop noise is illustrated in Fig. 18. The noise within the audio band from 300 Hz to 20 KHz shows less than -75 dBV. Fig. 19 is the transient measurement result of the dynamic supply conditioning PA with 1 KHz sinusoid output. The power supply VDD\_CHIP and VSS\_CHIP are switched when the signal is at the threshold points about +/-0.5 V. Neither obvious spike nor nonlinear distortion is superposed in the output waveform during the power supply transition between +/-1.8 V and +/-0.9 V. Table I summarizes

Fig. 18. Measured result of the click-pop noise power spectrum density.

Fig. 19. Transient measurement result of the dynamic supply conditioning mode.

the measurement results of this work and compares it with the state-of-the-art designs, showing that the proposed PA with dynamic transconductance compensation technique provides -85 dB THD+N, 106 dB signal dynamic range with only 0.6 mA static current consumption.

# V. CONCLUSION

This paper presents a low power Class-AB power amplifier using CMOS 55 nm process. By introducing a dynamic transconductance compensation technique, the bandwidth of the amplifier can be extended when a light loading is presented. The proposed technique is also valid for the dynamic supply conditioning (Class-G) mode operating with a single flying capacitor charge pump. The proposed power amplifier core circuit consumes only 0.35 mA static current and can provide 55 mW maximum output power and -85 dB THD+N, which shows state-of-the-art power efficiency and performance.

| SUMMARY OF MEASUREMENT RESULTS AND COMPARISON |         |          |           |                |          |            |                     |

|-----------------------------------------------|---------|----------|-----------|----------------|----------|------------|---------------------|

| Specifications                                | 2014[1] | 2006 [2] | 2009 [4]  | 2012 [6]       | 2013 [7] | 2012 [12]  | This work           |

| CMOS Process                                  | 40 nm   | 350 nm   | 130 nm    | 180 nm         | 180 nm   | 500 nm     | 55 nm               |

| Load capacitance                              | -       | 0~300 pF | 1pF~22 nF | -              | -        | 10 pF~5 nF | 5 pF~20 nF          |

| Closed-loop gain                              | -       | -        | -         | -              | -        | -4 V/V     | -6dB~6dB            |

| On-chip charge                                | Yes/Yes | No/Yes   | No/No     | -              | No/No    | -          | Yes/Yes             |

| pump and DAC                                  |         |          |           |                |          |            |                     |

| Supply voltage                                | 4.5 V   | 0.8 V    | 1.2 V     | 2.65 V         | 4.5 V    | 3 V        | 1.8 +/- 0.2 V       |

|                                               |         |          | /2.0 V    | $\sim 4.5 \ V$ |          |            |                     |

| Core static                                   | -       | -        | -         | -              | -        | -          | $0.35 \text{ mA}^1$ |

| current                                       |         |          |           |                |          |            | (with charge pump)  |

| Total static                                  | 0.84 mA | 3 mA     | 1 mA      | 1.15 mA        | 0.6 mA   | 1.43 mW    | 0.6 mA              |

| current                                       |         |          |           |                |          |            |                     |

| Output power                                  | 82 mW   | 28 mW    | 40 mW     | 60 mW          | 62 mW    | 93.8 mW    | 55 mW               |

| Dynamic range                                 | 100dB   | 88dB     | 92dB      | 111dB          | 108dB    | -          | $106 dB^2$          |

| THD+N                                         | -84dB   | -69dB    | -84dB     | -95dB          | -88dB    | -77.9 dB   | $-85 dB^3$          |

| FOM                                           | 21.69   | 11.67    | 33.33     | 19.68          | 22.96    | 65.5       | 50.93 <sup>4</sup>  |

TABLE I Summary of Measurement Results and Comparison

<sup>1</sup>10% power saving due to the proposed dynamic transconductance compensation scheme

<sup>2</sup> With 1KHz signal, 20Hz ~20KHz noise band, 0dB gain, 20 harmonics, 1 nF & 16 ohm load

<sup>3</sup>With 1KHz, -60dBV signal, 20Hz~20KHz noise band, 0dB gain, 20 harmonics, 1 nF & 16 ohm load

<sup>4</sup> FOM = Output power/(Supply voltage × Total static current)

#### REFERENCES

- [1] K. Abdelfattah, S. Galal, I. Mehr, A. J. Chen, C. Yu, M. Tjie, A. Tekin, X. Jiang, and T. L. Brooks, "A 40 nm fully integrated 82 mW stereo headphone module for mobile applications," *IEEE J. Solid-State Circuits*, vol. 49, pp. 1702–1714, 2014.

- [2] Q. Meng, K. Lee, T. Sugimoto, K. Hamashita, K. Takasuka, S. Takeuchi, U.-K. Moon, and G. C. Temes, "A 0.8 V, 88 dB dual-channel audio sigmadelta DAC with headphone driver," *Proc. Symp. VLSI Circuits (VLSIC)*, 2006, pp. 53–54.

- [3] G. Rincon-Mora, "Active capacitor multiplier in Miller-compensated circuits," *IEEE J. Solid-State Circuits*, vol. 35, pp. 26–32, 2000.

- [4] V. Dhanasekaran, J. Silva-Martinez, and E. Sanchez-Sinencio, "Design of three-stage class-AB 16 ohm headphone driver capable of handling wide range of load capacitance," *IEEE J. Solid-State Circuits*, vol. 44, pp. 1734–1744, 2009.

- [5] K. N. Leung and P. K. T. Mok, "Three-stage large capacitive load amplifier with damping-factor-control frequency compensation," *IEEE J. Solid-State Circuits*, vol. 35, pp. 221–230, 2000.

- [6] S. Galal, H. Zheng, K. Abdelfattah, V. Chandrasekhar, I. Mehr, A. J. Chen, J. Platenak, N. Matalon, and T. L. Brooks, "A 60 mW Class-G stereo headphone driver for portable battery-powered devices," *IEEE J. Solid-State Circuits*, vol. 47, pp. 1921–1934, 2012.

- [7] J. Chen, S. K. Arunachalam, T. L. Brooks, I. Mehr, F. Cheung, and H. Venkatram, "A 62 mw stereo class-G headphone driver with 108 dB dynamic range and 600 uA/channel quiescent current," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, 2013, pp. 182–183.

- [8] J.-J. Chen, H.-C. Lin, C.-M. Kung, Y.-S. Hwang, and J.-H. Su, "Integrated class-D amplifier with active current sensing suitable for alternating current switches," *IEEE Trans. Ind. Electron.*, vol. 55, pp. 3141–3149, 2008.

- [9] A. Nagari, E. Allier, F. Amiard, V. Binet, and C. Fraisse, "An 8 Ω 2.5 W 1%-THD 104 dB(A)-dynamic-range class-D audio amplifier with ultralow EMI system and current sensing for speaker protection," *IEEE J. Solid-State Circuits*, vol. 47, pp. 3068–3080, 2012.

- [10] M. Berkhout, L. Dooper, and B. Krabbenborg, "A 4  $\Omega$  2.65 W class-D audio amplifier with embedded DC-DC boost converter, current sensing ADC and DSP for adaptive speaker protection," *IEEE J. Solid-State Circuits*, vol. 48, pp. 2952–2961, 2013.

- [11] P. Roshankumar, P. Rajeevan, K. Mathew, K. Gopakumar, J. I. Leon, and L. G. Franquelo, "A five-level inverter topology with single-DC supply by cascading a flying capacitor inverter and an H-bridge," *IEEE Trans. Power Electron.*, vol. 27, pp. 3505–3512, 2012.

- [12] C. Mohan and P. M. Furth, "A 16-ohm audio amplifier with 93.8-mW peak load power and 1.43-mW quiescent power consumption," *IEEE Trans. Circuits Syst. II, Express Briefs*, vol. 59, pp. 133–137, 2012.

- [13] C. Wang, M. Vaidyanathan, and L. E. Larson, "A capacitancecompensation technique for improved linearity in CMOS class-AB power amplifiers," *IEEE J. Solid-State Circuits*, vol. 39, pp. 1927–1937, 2014.

- [14] K. N. Leung and P. K. T. Mok, "Nested miller compensation in low-power CMOS design," *IEEE Trans. Circuits Syst. II, Express Briefs*, vol. 48, pp. 388–394, 2001.

- [15] X. Peng and W. Sansen, "Nested feed-forward Gm-stage and ing resistor plus nested-Miller compensation for multistage amplifiers," *Proc. IEEE* 2002 Custom Integr. Circuits Conf., 2002, pp. 329–332.

- [16] Z. Yan, P.-I. Mak, M. Law, and R. P. Martins, "A 0.016-mm2 144-uW three-stage amplifier capable of driving 1-to-15 nF capacitive load with > 0.95-MHz GBW," *IEEE J. Solid-State Circuits*, pp. 527–540, 2013.

- [17] A. Nagari, E. Allier, F. Amiard, V. Binet, and C. Fraisse, "An 8 2.5 W 1%-THD 104 dB(A)-dynamic-range class-D audio amplifier with an ultra-low EMI system and current sensing for speaker protection," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, 2012, pp. 92–93.

- [18] B. K. Ahuja, "An improved frequency compensation technique for CMOS operational amplifiers," *IEEE J. Solid-State Circuits*, vol. 18, pp. 629–633, 1983.

- [19] Y. Mohammad, "Hybrid cascode compensation for two-stage CMOS Opamps," *IEICE Trans. Electron.*, vol. 88, pp. 1161–1165, 2005.

- [20] J. Kang, F. She, P. Jie, and Z. Weidong, "Audio testing technology research," Proc. 10th Int. Conf. Electron. Meas. Instrum. (ICEMI), 2011, pp. 24–28.

- [21] E. Fong and R. Zeman, "Analysis of harmonic distortion in single-channel Mos integrated circuits," *IEEE J. Solid-State Circuits*, vol. SSC-17, pp. 83–86, 1982.

- [22] K.-H. Chen and Y.-S. Hsu, "A high-PSRR reconfigurable class-AB/D audio amplifier driving a hands-free/receiver 2-in-1 loudspeaker," *IEEE J. Solid-State Circuits*, vol. 47, pp. 2586–2603, 2012.

Fang Tang (S'07–M'14) received the B.S. degree from Beijing Jiaotong University, China, in 2006. He received the M.Phil and Ph.D degrees from Hong Kong University of Science and Technology in 2009 and 2013, respectively, where he worked as Research Associate. Since the end of 2013, he is a Distinguished Research Fellow in the College of Communication Engineering, Chongqing University (CQU), China. Currently, Dr. Tang is the Associate Director of Chongqing Engineering Laboratory of High Performance Integrated Circuits and leads the

Smart Integrated Circuits and Systems Laboratory (SIS LAB) in Chongqing University. His research interests include mixed-signal circuit design for advanced smart integrated circuit and system. He has published over 40 articles in journals, conference proceedings and designed over 10 chips.

Shiping Li received the B.Sc. degree in the College of Microelectronics from Xidian University, Xian, China, in 2014. He is currently working toward the M.S. degree in the College of Communication Engineering, Chongqing University (CQU), China. His research interest is the design for mixed-signal integrated circuits.

Xichuan Zhou (S'06–M'13) received the B.S. and Ph.D. degrees from Zhejiang University, China, in 2005 and 2010, respectively. Since the end of 2010, he is an Associate Professor and the Assistant Dean of the College of Communication Engineering, Chongqing University (CQU), China. His research interests include large-scale system design, optimization and application. He has published over 10 articles in journals and conference proceedings.

**Bo Wang** (S'16) received the B.Sc. degree in the Department of Electrical Engineering from Zhejiang University, Hangzhou, China, in 2010 and the M.Phil degree in the Department of Electronic and Computer Engineering from Hong Kong University of Science and Technology (HKUST), in 2012, where he received the Ph.D degree in 2015. He is currently a Postdoc in Massachusetts Institute of Technology (MIT), Cambridge, MA, USA. His research interests include smart CMOS temperature sensors and sensor interfaces, on-chip process compensation tech-

niques, and heterogeneous sensor integration.

Amine Bermak (M'99–SM'04–F'12) received both his MEng. and Ph.D. degrees in electronic engineering from Paul Sabatier University, Toulouse, France, in 1994 and 1998, respectively. In November 1998, he joined Edith Cowan University, Perth, Australia, as a Research Fellow working on smart vision sensors. In January 2000, he was appointed Lecturer and promoted to Senior Lecturer in December 2001. In July 2002, he joined the Electronic and Computer Engineering Department of Hong Kong University of Science and Technology (HKUST), where he is

currently a full Professor and ECE Associate Head for postgraduate education and research. He has also been serving as the Director of Computer Engineering as well as the Director of the Master Program in IC Design. He is also the founder and the leader of the Smart Sensory Integrated Systems Research Lab at HKUST. He was a member of the senate committee at HKUST.

Prof. Bermak has been very actively involved in many research and industrial projects in collaboration with Motorola-France, 3D plus-France, British Aerospace-UK, Intelligent Pixel Inc. C USA. His research interests are related to VLSI circuits and systems for signal, image processing, sensors and microsystems applications. He has published over 250 articles in journals, book chapters and conference proceedings and designed over 30 chips. He is a member of the IEEE Circuits and Systems Society committee on Sensory Systems as well as BIOCAS. He has served on the editorial board of IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS and the Sensors Journal. He is also currently serving on the editorial board of IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS and IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—PART II: EXPRESS BRIEFS. He is the Guest Editor of the November 2010 special issue in IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS. Prof. Bermak is an IEEE Distinguished Lecturer.

Shengdong Hu received Ph.D. degrees from University of Electronic Science and Technology of China, in 2010. He is an Associate Professor in the College of Communication Engineering, Chongqing University (CQU), China. His research interests include power electronics, semiconductor devices. He has published over 10 journals.